Источник: А.Долгий. Микросхемы памяти с интерфейсом I2C. — Радио, 2001, №2, с.24-26, — Радио, 2001, №3, с.

Шина I2С широко используется, став стандартом для многих бытовых и промышленных устройств.

Версия 1.0 стандарта (спецификации) на шину I2С появилась лишь в 1992 г. Применявшийся ранее “стандартный» режим с ограничением скорости передачи значением 100 Кбит/с был дополнен «быстрым» (Fast-mode) с допустимой скоростью до 400 Кбит/с, а кроме семиразрядных адресов подключаемых к шине устройств, были разрешены и десятиразрядные. Версия 2.0, вышедшая в 1998 г., добавила «высокоскоростной» (High Speed, Hs-mode) режим со скоростью до 3.4 Мбит/с. С января 2000 г. действует спецификация версии 2.1. в которой уточнены некоторые положения предыдущей.

К шине I2С можно подключать до 128 (в варианте с десятиразрядным адресом — до 1024) устройств. Их двунаправленные входы/выходы SCL (Serial Clock) и SDA (Serial Data) с открытыми коллекторами подключают к одноименным линиям параллельно. Линии нагружены резисторами, соединенными с источником питания. Номиналы резисторов и напряжение питания спецификация не устанавливает. Необходимо лишь, чтобы ток короткого замыкания любой из линий на общий провод не превышал 3 мА, а ёмкость с учетом подключенных абонентов — 400 пф.

Одно из устройств служит ведущим (master), остальные — ведомыми (slave). Первое генерирует синхроимпульсы SCL и управляет всем обменом по шине. Ведомые только в ответ на запросы ведущего принимают от него или передают ему данные.

Общее представление о порядке передачи информации дают временные диаграммы, показанные на рис. 1. Исходное состояние шины — высокие логические уровни на линиях SDA и SCL. Чтобы начать сеанс обмена данными, ведущий, не меняя состояния линии SCL, устанавливает низкий уровень на линии SDA, а затем — такой же уровень на линии SCL. Это команда СТАРТ. Получив ее, все ведомые должны приготовиться к приему.

Передача информации — побитная. При низком уровне SCL, поддерживаемом ведущим, передатчик (во время передачи первого байта это тоже ведущий. но в дальнейшем им может стать и любой из ведомых) устанавливает на линии SDA уровень, соответствующий значению передаваемого бита (лог. 1 — высокий, 0 — низкий). Затем ведущий устанавливает на линии SCL высокий уровень, а по истечении времени, отведенного приемнику для принятия информации, вновь сменяет его низким. Данная процедура повторяется для каждого передаваемого бита. Ведущий завершает сеанс командой СТОП — сменой низкого уровня на линии SDA высоким при таком же уровне на линии SCL.

Во всех ситуациях, кроме подачи команд СТАРТ и СТОП, не допускается смена уровня на линии SDA при высоком уровне SCL. Не рекомендуется и одновременное изменение состояния этих линий — временной «зазор” должен составлять не менее 0,3 (0,1) мкс.

Частота повторения импульсов SCL — не более 100 (400) кГц при длительности импульса или паузы не менее 4,7 (1.2) мкс. В скобках указаны нормативы “быстрого» режима.

Временные диаграммы, изображенные на рис. 2. показывают, каким образом происходит передача байта. Ей предшествует команда СТАРТ или рассмотренный далее бит подтверждения приема предыдущего байта. Первым передают старший разряд байта, последним — младший, после чего принявшее байт устройство подтверждает этот факт, установив на линии SDA низкий байта начинается передача следующего или подается команда СТОП.

Семь старших битов байта, обязательно передаваемого ведущим вслед за командой СТАРТ, представляют собой адрес ведомого, с которым он намерен установить связь. Если среди подключенных к шине есть исправное устройство с таким адресом, оно должно подтвердить прием и подготовиться к дальнейшим действиям. Все остальные ведомые, не опознав своего адреса, отключаются до следующей команды СТАРТ.

Полный список зарезервированных за различными устройствами адресов ведомых шины ГС фирма Philips держит в секрете, мотивируя это тем, что в противном случае неизбежен «самозахват» свободных адресов. Известно, что микросхемам памяти выделены восемь адресов с 1010000 по 1010111, хотя некоторые из них могут быть настроены на коды и вне этого диапазона.

Младший восьмой бит первого байта — признак направления передачи. Если его значение — лог. 0 (низкий уровень), информация в данном сеансе будет записываться/передаваться от ведущего к ведомому, в противном случае первый намерен читать данные, передаваемые ведомым. Процесс передачи всех последующих байтов аналогичен описанному выше, их число за сеанс не ограничено, однако смена направления передачи до завершения сеанса не предусмотрена.

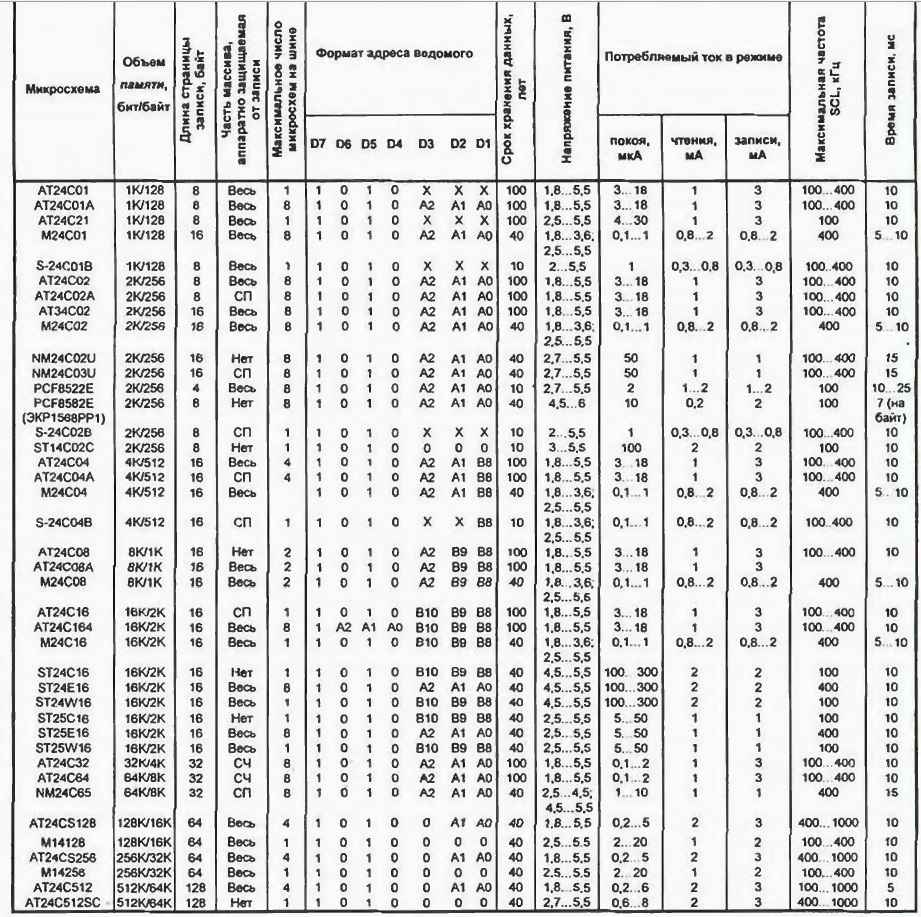

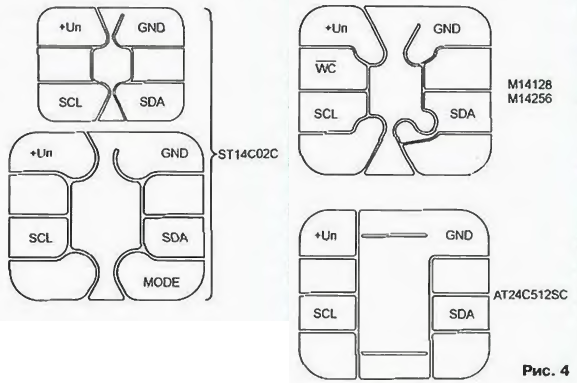

Параметры микросхем памяти с интерфейсом I2С приведены в табл. 1. Все они — многократно репрограммируемые ПЗУ с электрическим стиранием и записью данных. Список далеко не исчерпывающий.

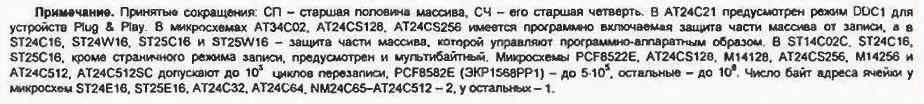

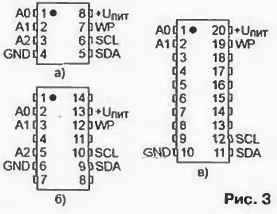

Микросхемы одного и того же типа выпускают в корпусах различных размеров и конструкций. В большинстве случаев — с восемью штыревыми или планарными выводами, назначение которых независимо от типоразмера корпуса и размещенного в нем кристалла почти всегда одинаково и соответствует показанному на рис. З.а. Если число выводов более восьми, «лишние” оставляют свободными. Возможные варианты корпусов показаны на рис. 3, б и в. Микросхемы, предназначенные для пластиковых карт (например, телефонных), изготовляют в виде плоских модулей. Их выводы — довольно сложной формы (рис. 4). Для соединения с внешними цепями необходимо специальное контактное устройство.

Напряжение питания микросхем — от 1,8…4,5 (в зависимости от типа и буквенного индекса в обозначении) до 5,5 В. Как правило, с уменьшением напряжения питания снижаются потребляемый ток и быстродействие. Нагрузочная способность выхода SDA — 3…5 мА, входной ток и ёмкость любого входа не превышают соответственно 1 мкА и 4…8 пФ.

Входы, к которым не подключены внешние цепи, приобретают нулевой потенциал за счет специально предусмотренных в микросхемах внутренних утечек. Нулевыми следует считать и логические значения задаваемых этими входами управляющих сигналов. Приемники сигналов SDA и SCL представляют собой триггеры Шмитта и снабжены фильтрами, подавляющими импульсы короче 0,1 мкс (это повышает помехоустойчивость).

Хотя спецификацией шины I2С ведомому предоставлено право «тормозить» обмен данными, принудительно удерживая на линии SCL низкий уровень на время. необходимое для выполнения каких-либо внутренних операций, микросхемы памяти этой возможностью не пользуются, их вывод SCL — только вход в отличие от двунаправленного SDA.

Логическими уровнями, поданными на входы АО—А2, обычно задают три младших разряда адреса микросхемы как ведомого шины I2С . В справочных данных некоторых микросхем их называют «входами выбора кристалла», хотя это и не совсем соответствует выполняемой функции. Старшие четыре разряда адреса микросхемы памяти всегда содержат двоичную комбинацию 1010. Исключение — микросхема АТ24С164. У нее старший разряд — всегда лог. 1, далее следуют три, значения которых задают логическими уровнями на входах А0—А2, и три старших разряда адреса ячейки памяти.

Адресные входы задействованы далеко не во всех микросхемах, иногда они вовсе не предусмотрены. Такая микросхема откликается на адрес с любыми значениями младших разрядов. В других случаях в них подразумеваются лог. 0. Если объем памяти превышает 256 байт, отказываются от одного или нескольких входов А0—А2 и отдают соответствующие им разряды адреса ведомого старшим битам адреса ячейки памяти. В табл. 1 такие биты обозначены буквами В с цифровыми индексами. Если и этих разрядов не хватает, им возвращают прежнее назначение, но увеличивают число байтов, отведенных на передачу адресов ячеек памяти. Иногда неиспользованные в качестве адресных входы служат для управления положением в массиве памяти и размером зоны, защищенной от случайного или преднамеренного изменения хранящихся там данных.

Вход WP (Write Protect) предназначен для управления защитой записанных в микросхему данных. Иногда его обозначают как WC (Write Control) или ![]() , что совершенно не влияет на его функцию. Если этот вывод оставлен свободным или соединен с общим проводом, можно изменять содержимое любых ячеек. При высоком логическом уровне весь массив или его часть защищены от стирания и записи. В последнее время выпускают микросхемы, в которых предусмотрены участки памяти, запись в которые можно заблокировать и другими способами, например, командами ведущего.

, что совершенно не влияет на его функцию. Если этот вывод оставлен свободным или соединен с общим проводом, можно изменять содержимое любых ячеек. При высоком логическом уровне весь массив или его часть защищены от стирания и записи. В последнее время выпускают микросхемы, в которых предусмотрены участки памяти, запись в которые можно заблокировать и другими способами, например, командами ведущего.

Логическим уровнем на входе MODE (при его наличии) переключают режимы записи данных. Если он оставлен свободным или соединен с общим проводом, действует мультибайтный режим, в противном случае—страничный. Особенности этих режимов будут рассмотрены далее. Микросхемы, не имеющие названного входа, работают только в страничном режиме записи. Один из вариантов микросхемы ST14C02C (рис. 4) выпускают без внешнего вывода MODE, который на ее кристалле предусмотрен, но оставлен не подключенным. В результате всегда включен мультибайтный режим.

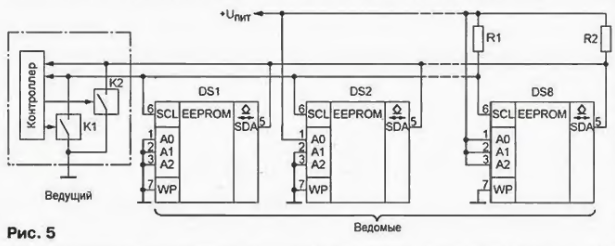

Схема соединений микросхем памяти с линиями шины показана на рис. 5.

В зависимости от числа действующих входов А0—А2 их может быть от одной до восьми, причем комбинации логических уровней на этих входах у каждой из них должны быть различными. Так как максимальная длительность импульсов на шине не ограничена, ключами К1 и К2 могут служить даже обычные выключатели, коммутируемые вручную. Подобный вариант пригодится, если, например, необходимо «подручными средствами» прочитать или записать несколько байтов данных. Визуально определить состояние линий позволят светодиоды, включенные последовательно с резисторами R1 и R2.

Но обычно в роли ведущего все-таки выступает микроконтроллер или специализированное устройство. Ключами К1 и К2 служат транзисторы выходных каскадов двунаправленного порта. Каждая из линий шины занимает всего один разряд подобного порта. В противном случае на нее приходится расходовать по одному разряду обычных однонаправленных портов ввода и вывода, дополняя их ключами на биполярных или полевых транзисторах или логическими элементами с открытым коллектором (стоком).

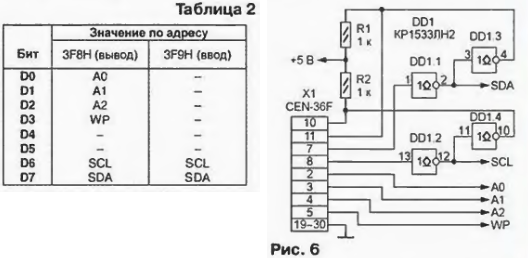

Примером может служить адаптер для подключения устройств с интерфейсом I2С к параллельному порту персонального компьютера. Реализованное в нем распределение сигналов по битам регистров порта LPT1 приведено в табл. 2, а принципиальная схема показана на рис. 6.

Разъем Х1 — розетка CEN-36E обычно устанавливаемая на принтерах, или вилка DB-25M (с общим проводом соединяют ее контакты 18—25). В зависимости от типа разъема адаптер либо связывают с компьютером стандартным «принтерным» кабелем CENTRONICS, либо стыкуют непосредственно с розеткой LPT на системном блоке (в этом случае не обязательны элементы DD1.3, DD1,4 и резисторы R1, R2: первые —заменяют перемычками, вторые — исключают). В обслуживающей программе наличие или отсутствие инверторов в цепях SDA и SCL должно быть обязательно учтено.

Рассмотрим процедуры «общения» ведущего с микросхемами памяти. Прежде всего, он обязан сформировать на шине команду СТАРТ, вслед за которой послать байт с адресом ведомого и установленным признаком записи (лог. 1 в младшем разряде). Получив подтверждение приема, ведущий продолжает передачу, посылая один или два байта адреса ячейки памяти. Прием каждого из них должен быть подтвержден ведомым. В отличие от привычного программистам принятого в IBM PC порядка первым в данном случае передается байт со старшими разрядами адреса.

Дальнейшие действия зависят от того, намерен ли ведущий читать данные, хранящиеся в массиве памяти ведомого, или записывать их туда. Для записи одного или нескольких байт их достаточно передать вслед за адресом. Первый попадет в заданную ячейку, после чего внутренний контроллер микросхемы памяти автоматически инкрементирует (увеличивает на единицу) адрес. Поэтому повторять его передачу не требуется. Следующий байт будет направлен в следующую ячейку и так далее до верхней границы страницы записи (в соответствующем числе младших разрядов адреса ячейки — все единицы), после чего заполнение страницы продолжится с нижней границы (в младших разрядах — все нули). Число байт данных, передаваемых в одном сеансе, не ограничено, но сохранятся лишь последние из них в количестве, не превышающем длины страницы.

Страничная запись значительно сокращает время, требуемое для перезаписи всего массива памяти или большей его части. Однако пользоваться ею следует осторожно. Дело в том, что многие микросхемы, взаимозаменяемые по остальным параметрам, различаются именно длиной страницы записи. В ответственных случаях рекомендуется предварительно определить ее фактическую длину. Достаточно послать ведомому для записи заведомо больше данных, чем может поместиться на странице наибольшей длины, и проверить. в каких ячейках информация действительно изменилась.

Кроме страничной записи, иногда предусматривается и мультибайтная, отличие которой в том, что адреса последовательно записываемых ячеек могут находиться на смежных страницах, пересекая их границу. В одном сеансе передают данные максимум для восьми, реже —16 ячеек, причем «перебор» запрещен.

В любом случае после передачи и подтверждения приема всех данных для программирования ведущий подает команду СТОП, запускающую в микросхеме внутренний автомат записи. Продолжительность выполняемой им процедуры не зависит от числа изменяемых байтов: автомат всегда стирает и вновь записывает всю страницу. Интересно, что происходит это даже в тех случаях, когда соответствующая область памяти защищена от записи. Данные в ней будут стерты и повторно записаны без изменений. Так что, отключив питание в неподходящий момент, защищенную информацию можно испортить. Если данные переданы в мультибайтном режиме и находятся на разных страницах, продолжительность записи удваивается — автомат программирует две страницы.

До окончания процедуры программирования микросхема памяти нe реагирует ни на какие внешние сигналы и в течение этого времени на повторные обращения следующего по её адресу не откликается. Этим пользуются для определения момента завершения программирования.

Перед чтением данных не требуется обязательно указывать адрес ячейки. Если ведущий обращается к микросхеме памяти, установив в младшем бите байта адреса ведомого признак чтения (лог. 1), в ответ ему будет передан байт из ячейки, следующей за той, с которой выполнялась последняя операция записи или чтения, после чего счетчик адреса будет автоматически инкрементирован. Выдача ведомым данных на линию SDA синхронизируется импульсами SCL, генерируемыми ведущим. Он же обязан подтвердить прием.

Продолжая посылать импульсы SCL, ведущий может последовательно и неоднократно прочитать весь массив данных. Возврата к началу страницы на ее границе при чтении не происходит, а за адресом последней ячейки всего массива следует нулевой. Сигнал окончания чтения — отсутствие подтверждения ведущим приема последнего или единственного байта данных и следующая за этим команда СТОП. Подавать такую команду после подтвержденного приема опасно, так как в некоторых ситуациях этим можно ошибочно запустить автомат записи.

При необходимости адрес читаемой ячейки задают в явном виде следующим образом. Прежде всего ведущий обращается к ведомому с признаком записи и посылает ему один или два байта адреса ячейки. Получив подтверждение, он немедленно (без команды СТОП) посылает новую команду СТАРТ, а за ней — адрес ведомого с признаком чтения и выполняет описанную выше процедуру. Первым ему будет передан байт из ячейки с указанным адресом.

Еще одну возможность прочитать данные предоставляет микросхема АТ24С21, предназначенная для компьютерных периферийных устройств «Plug & Play». Во многих из них выводы SDA и SCL этой или подобной ей микросхемы соединены соответственно с выводами 12 и 15 внешнего 15-контактного разъема (VGA монитора). Иногда через вывод 9 того же разъема на микросхему можно подать питание и прочитать хранящиеся в ней данные и даже изменить их.

Сразу после включения питания при высоком уровне на линии SCL микросхема АТ24С21 входил в режим DDC1. В ответ на синхронизирующие импульсы, подаваемые на вывод 7, называемый в данном случае VCLK (в мониторе он соединен с выводом 14 интерфейсного разъема), микросхема побитно выдает на линию SDA все содержимое своей памяти. Хотя подтверждать прием в режиме DDC1 не требуется, каждый девятый импульс VCLK — холостой, ему соответствует высокий уровень на линии SDA. Передача повторяется циклически (за младшим битом последнего байта следует старший первого) неограниченное число раз.

Разобраться в этом потоке — нелегкая задача для приемника. Несколько облегчает ее то, что во время действия первых после включения питания восьми импульсов VCLK микросхема анализирует состояние шины SDA, воспринимая его как адрес ячейки, с которой следует начать передачу данных после холостого девятого импульса. Запись в микросхему, находящуюся в режиме DDC1, невозможна.

Режим DDC2, во всем совпадающий с I2С , включают сменой высокого уровня на линии SCL низким. После этого вход VCLK превращается в обычный WP и управляет защитой массива памяти от записи. Вернуться в режим DDC1 можно только коммутацией питания.

У некоторых микросхем предусмотрена возможность программного включения защиты части массива данных от записи. Одна из них — АТ34С02. Кроме обычного адреса ведомого, начинающегося двоичной комбинацией 1010, у нее имеется специальный, начинающийся комбинацией 0110, за которой следуют биты со значениями. совпадающими с логическими уровнями на входах А0—А2. Если микросхема подтверждает прием этого адреса, переданного с признаком чтения, — вам повезло, защита еще не включена. Приём обращения по тому же адресу с признаком записи микросхема подтвердит при условии, что на вывод WP подан высокий логический уровень. И все… Больше она на этот адрес никогда не откликнется, и изменить что-либо в младшей половине массива памяти уже не удастся. Защитой старшей половины массива продолжает управлять вход WP.

Аналогичная операция с микросхемами AT24CS128 или AT24CS256 сложнее. Она защитит старшие 258 байт массива. На входах А0 и А1 следует установить любые, но одинаковые логические уровни. Затем передать по шине последовательность

- СТАРТ

- 10101100

- 11ХХХХХХ

- ХХХХХХХХ

- ХХХХХХХХ

- СТОП

Значения битов, обозначенных буквой X, безразличны. Как и в предыдущем случае, включенную однажды защиту невозможно отключить. Поэтому, не будучи полностью уверенным в том. что изменять данные в защищенной области никогда не потребуется, экспериментировать не стоит.

В заключение — несколько слов о том, как привести микросхему с интерфейсом I2С в исходное состояние. Обычно эту операцию автоматически выполняет внутренний контроллер после включения питания. Она может занимать довольно много времени (до 200 мс). В связи с этим спешить с записью или чтением не следует, лучше дать микросхеме время “прийти в себя”. Если нормальная работа нарушилась в результате сбоя или ошибочных действий ведущего, ее нередко удается восстановить, не выключая питания. Для этого достаточно подать на линию SDA со стороны ведущего высокий уровень и сформировать девять импульсов аналогичного уровня на линии SCL. Убедившись, что ни одно из ведомых устройств не поддерживает на линии SDA низкий уровень, можно подавать команду СТАРТ. В неопределенных ситуациях ни в коем случае нельзя пользоваться командой СТОП, так как это чревато записью случайных данных по случайным адресам.